Features

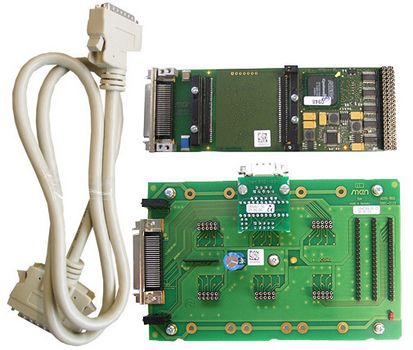

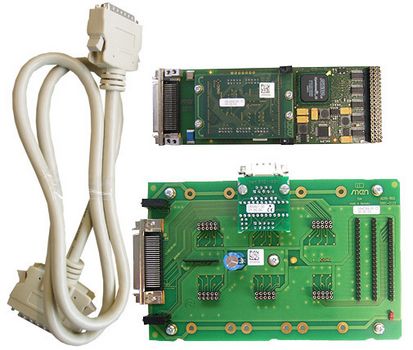

- 1 Main M-Module M199 for USM Universal Submodules:

- 1 FPGA 33,216 LE

- 32 MB DDR2 SDRAM, 8 MB Flash

- 1 bare USM module US0

- 1 evaluation board with RS232 debug interface

- 1 FPGA development package:

- Main bus interface

- Memory control

- Nios softcore

- Wishbone/Avalon bridges

- For user-defined I/O

- 1 SCSI cable

- -40 to +85 °C with qualified components